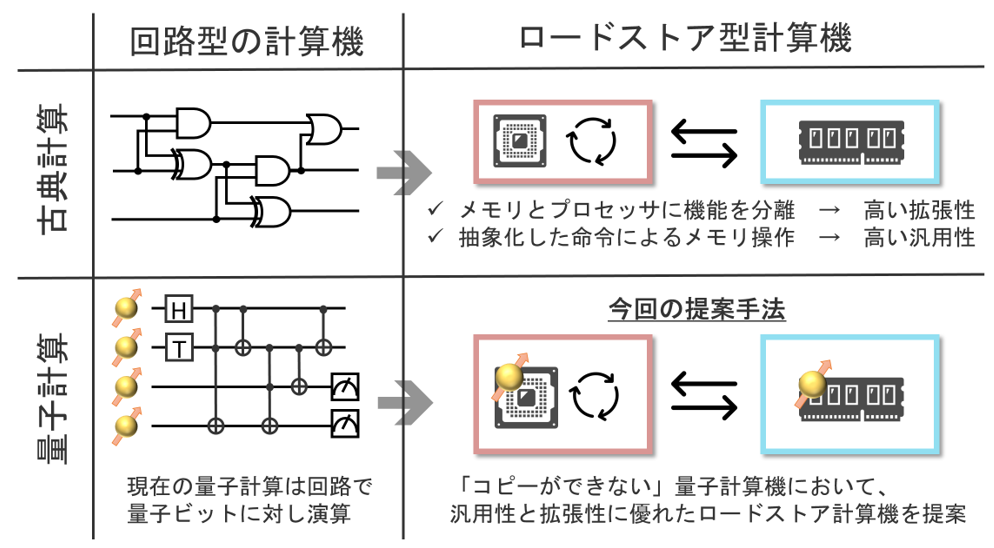

Proposal for a new quantum computer architecture that separates the memory and processor

News 2025/03/05

Takumi Kobori, a graduate student (an intern at Nippon Telegraph and Telephone Corporation at the time) and Professor Synge Todo of the Graduate School of Science at The University of Tokyo, Researchers Yasunari Suzuki and Yuuki Tokunaga of Nippon Telegraph and Telephone Corporation, Research Fellow Yosuke Ueno of the RIKEN Quantum Computer Science Institute, and Associate Professor Teruo Tanimoto of the Graduate School of Systems Information Science, Kyushu University, have proposed a new architecture for error-tolerant quantum computation that applies the basic design of conventional computers to quantum computers. Associate Professor Teruo Tanimoto and his research group have proposed a new architecture for error-tolerant quantum computation that applies the basic design of conventional computers, the load-store computing concept, to quantum computers. This technology is expected to accelerate the early realization of useful quantum computation by enabling high portability of programs (ease of migration to other environments) and utilization of highly efficient quantum hardware. The results were presented at The 31st IEEE International Symposium on High-Performance Computer Architecture (HPCA2025), which is being held from March 1, 2025.

See below for more information.

- Todo Group:https://exa.phys.s.u-tokyo.ac.jp/

- UTokyo FOCUS:https://www.s.u-tokyo.ac.jp/en/press/10693/

- Conference Presentation:

"LSQCA: Resource-Efficient Load/Store Architecture for Limited-Scale Fault-Tolerant Quantum Computing", The 31st IEEE International Symposium on High-Performance Computer Architecture (HPCA2025)