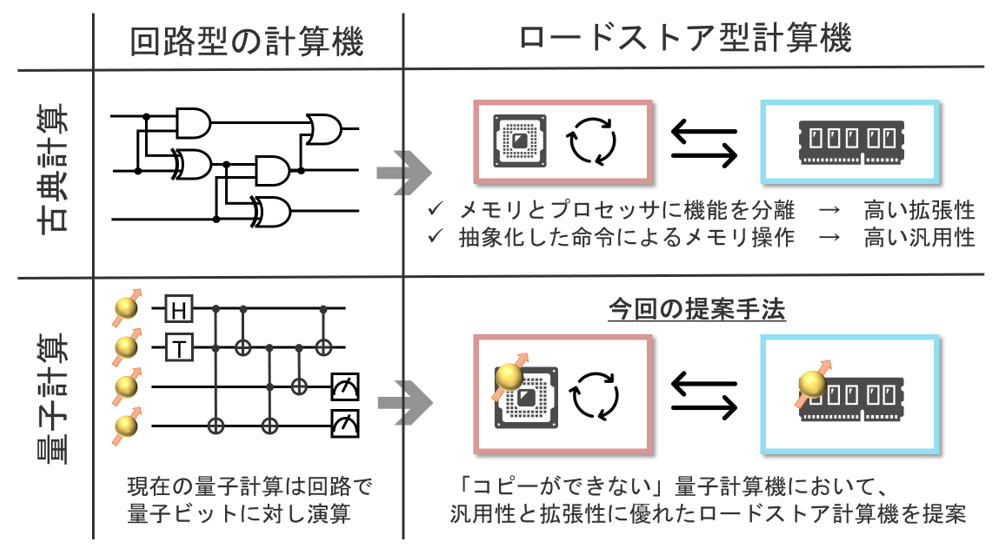

メモリとプロセッサを分離した新たな量子コンピュータのアーキテクチャを提案

研究成果 2025/03/05

東京大学大学院理学系研究科小堀拓生大学院生(当時日本電信電話インターン生)と藤堂眞治教授、日本電信電話株式会社の鈴木泰成研究員と徳永裕己研究員、理化学研究所量子コンピューター研究センターの上野洋典基礎科学特別研究員、そして九州大学大学院システム情報科学研究院の谷本輝夫准教授らによる研究グループは、従来の計算機の基本設計であるロードストア型計算機の考え方を量子計算機に適用した、新たな誤り耐性量子計算のアーキテクチャを提案しました。本技術は、プログラムの高い移植性(他の環境への移行のしやすさ)と高効率な量子ハードウェアの活用を可能とするものであり、有用な量子計算の早期実現を加速することが期待されます。

詳細については、以下をご参照ください。

- 理学系研究科 プレスリリース:https://www.s.u-tokyo.ac.jp/ja/press/10693/

- 論文情報:

The 31st IEEE International Symposium on High-Performance Computer Architecture (HPCA2025) にて "LSQCA: Resource-Efficient Load/Store Architecture for Limited-Scale Fault-Tolerant Quantum Computing" と題し発表 - 藤堂研究室:https://exa.phys.s.u-tokyo.ac.jp/