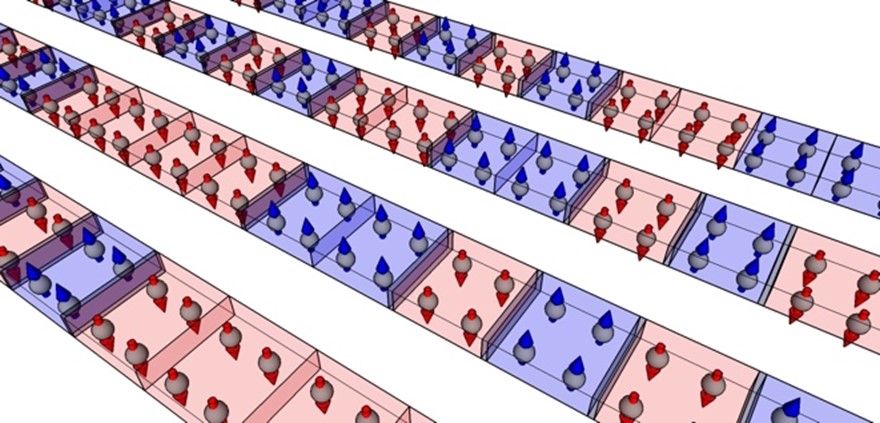

レーストラックメモリのビットエラー率決定に成功

研究成果 2024/10/30

東京大学大学院理学系研究科の石橋未央特任研究員(研究当時、現:東北大学材料科学高等研究所助教)、中辻知教授、林将光准教授らの研究グループは、産業技術総合研究所の薬師寺啓研究チーム長(研究当時、現:産業技術総合研究所総括研究主幹)のグループ、日本大学理工学部電子工学科の塚本新教授と共同で、レーストラックメモリの重要な性能指標であるデジタル情報のビット操作のエラー率を決定する手法を確立しました。ストレージクラスの次世代磁気メモリとして実用化が期待されている「レーストラックメモリ」の研究開発において、デジタル情報の書き込み、読み取り操作を実証する報告は多数あるものの、メモリ動作の信頼性を調べるアプローチはこれまでに確立されていませんでした。そこで本研究ではビット操作のエラー率を決定する新たな性能評価手法を確立しました。 フェリ磁性体細線を用いたレーストラックメモリを作製し、ナノ秒程度の電流パルスを使ってビット位置を制御する操作を繰り返し、ビット位置のばらつきからビットエラー率を求めました。その結果、ビット位置操作に用いる電流パルスが十分に大きい時に、連続する操作のビットエラー率に相関がないことがわかり、レーストラックメモリの開発に大きく弾みがつく結果が得られました。

詳細については、以下をご参照ください。